DATASHEET

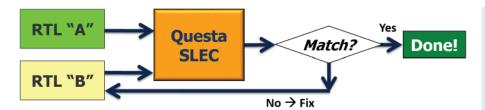

The Questa SLEC app uses formal analysis to exhaustively compare two blocks of RTL code, identifying any differences in the output behavior of the two designs for all inputs, and for all time.

### When an Exhaustive Comparison Is Essential

Quite a few high-value verification tasks involve the comparison of a circuit to a close equivalent that's been modified in a small, yet operationally critical way. For example, sometimes new logic is required to reduce dynamic power consumption, an ECO is needed at the last minute, or the impact of stuck-at or transient faults must be evaluated. While each of these tasks can be addressed with RTL simulation, doing so can take weeks — even months — of testbench development and simulation debug. Even worse, the results from even the most well-designed constrained-random simulation environment will not be exhaustive, leaving the door open for functional bugs that were unintentionally created by the added logic.

## Automated, Exhaustive, Sequential Logic Equivalence Checking

A sequential logical equivalence check (SLEC) formally verifies that two sequentially different designs are functionally equivalent. The Questa® SLEC app performs an exhaustive, formal-based analysis of two RTL designs in only a few hours — even minutes — depending on the design sizes and parameters. This frees the user from having to manually create and maintain testbenches and re-run massive, time and resource intensive simulation regression suites.

In particular, the following verification use cases dramatically benefit from a Questa SLEC analysis:

- Design optimization (state machine optimization, pipeline reordering, etc.)

- ISO26262-related fault/single event upset (SEU) safety mechanism verification

- Bug fix and ECO verification: avoiding time consuming re-simulation after making minor changes

- Low power clock gating logic insertion

All discrepancies are summarized in concise reports so users can quickly determine the severity of any issues that are identified.

**Note:** Pure logic equivalency checking (LEC) tools (like Mentor's FormalPro™) are for flows where the DUTs being compared have the exact same number of states — mainly for the purpose of verifying that the synthesis of RTL into gates was done correctly. In contrast, Questa SLEC is checking all sequential behaviors and, hence, can check that any modifications to the RTL do not affect the outputs.

#### **FEATURES AND BENEFITS:**

# Easy to Set Up and Use

- Automated hierarchy, instance, and signal name-mapping

- Quick root-cause debug guides users directly to source of an issue

- No knowledge of formal or assertion languages is required

- No testbench needed, enabling verification to start early in the design phase, before a simulation testbench is ready

- Powerful Tcl API for custom reports and flows

### **Automated, Exhaustive Analysis**

- Runs deep formal analysis on automatically mapped and correlated RTL designs to compare their behaviors for all inputs and all time

- Exhaustive approach means the analysis traverses the entire state space, revealing unexpected corner-cases that can be missed by other verification methods

- Checks all sequential behaviors, enabling comparison of IPs with unrelated state encodings

## **Benefits and Highlights**

**Ease of set up and use** — Set up is expedited by enabling users to account for trivial mismatches of net or instance names as well as arbitrary levels of hierarchy, before the analysis is launched. No testbench or knowledge of formal or assertion languages is required.

**Exhaustive results** — The Questa SLEC app uses formal engines under-the-hood to exhaustively compare the "specification" and "implementation" RTL, identifying any differences in the output behavior of the two designs for all inputs and for all time.

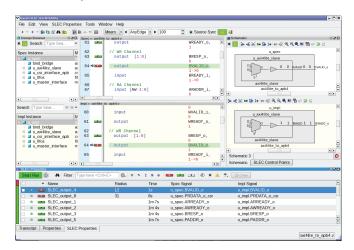

**Increased productivity** — All discrepancies are summarized with concise reports in an interactive GUI so users can quickly determine the root cause and severity of any issues that are identified. Plus, via the standard Tcl API users can easily tailor input, run-time, and output reports to address specific verification tasks.

Familiar visualization — The Questa SLEC debug GUI leverages familiar schematics and waveforms where appropriate. Waveforms and generated schematics show precisely the output discrepancies between the two DUTs, along with the responsible control signals and data pathways.

**High performance analysis** — Dedicated, applied research and engineering investment in Questa SLEC analysis technologies have produced continuous improvements in wall clock performance, memory usage, and storage consumption. This means Questa SLEC regularly exceeds demanding scalability and resource expectations.

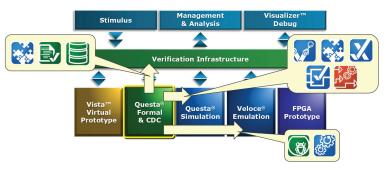

### **Enterprise Verification Platform**

Built upon several powerful technologies and tightly integrated with Veloce® emulation, the Enterprise Verification Platform™ transforms verification, dramatically increasing productivity and more efficiently managing resources. The Questa Formal and CDC solutions are integrated with simulation and emulation, sharing common features such as verification management, compilers, debuggers, and language support for SystemVerilog, Verilog, VHDL, and more.

This enables users to select the best application or tool for the job and then combine results from all the engines to dynamically track the progress of the entire verification program.

### For the latest product information, call us or visit: www.mentor.com

©2017 Mentor Graphics Corporation, all rights reserved. This document contains information that is proprietary to Mentor Graphics Corporation and may be duplicated in whole or in part by the original recipient for internal business purposes only, provided that this entire notice appears in all copies. In accepting this document, the recipient agrees to make every reasonable effort to prevent unauthorized use of this information. All trademarks mentioned in this document are the trademarks of their respective owners.

**Corporate Headquarters Mentor Graphics Corporation** 8005 SW Boeckman Road Wilsonville, OR 97070-7777 Phone: 503.685.7000 Fax: 503.685.1204

Sales and Product Information Phone: 800 547 3000 sales\_info@mentor.com

Silicon Valley **Mentor Graphics Corporation** 46871 Bayside Parkway Fremont, CA 94538 USÁ Phone: 510.354.7400 Fax: 510.354.7467

**North American Support Center** Phone: 800 547 4303

Europe Mentor Graphics Deutschland GmbH Arnulfstrasse 201 80634 Munich Germany Phone: +49.89.57096.0

Fax: +49.89.57096.400

**Pacific Rim** Mentor Graphics (Taiwan) 11F, No. 120, Section 2, Gongdao 5th Road Taiwan, ROC

HsinChu City 300. Phone: 886.3.513.1000 Fax: 886.3.573.4734

Japan Mentor Graphics Japan Co., Ltd. Gotenyama Trust Tower 7-35. Kita-Shinagawa 4-chome

Shinagawa-Ku, Tokyo 140-0001 Japan

Phone: +81.3.5488.3033 Fax: +81.3.5488.3004

MGC 05-17 1034630-w